The Origin of an Observation

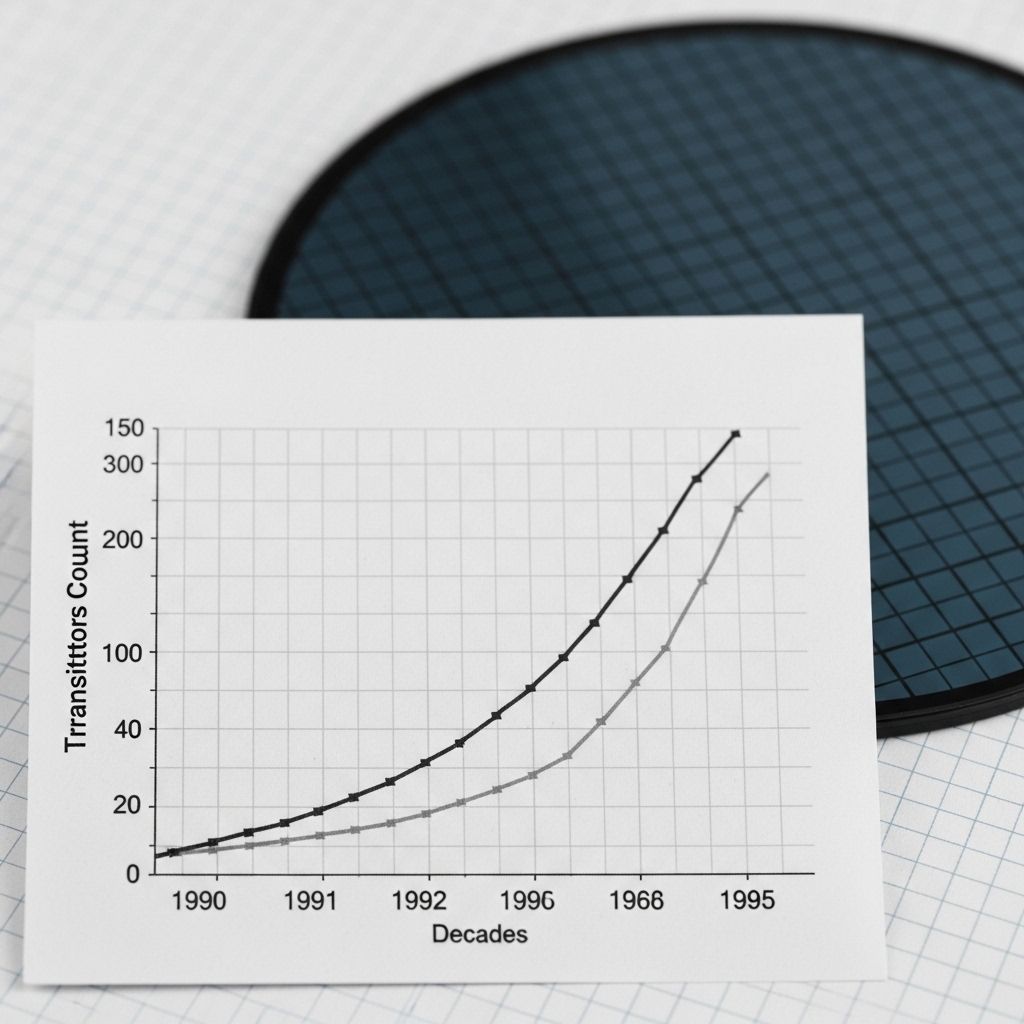

In April 1965, Gordon Moore — then director of research and development at Fairchild Semiconductor — published a paper in Electronics magazine titled "Cramming More Components onto Integrated Circuits." The central observation was deceptively simple: the number of components per integrated circuit had doubled roughly every year since the first commercially available planar integrated circuits appeared in 1961. Moore projected that this trend would continue for at least another decade.

In 1975, Moore revised his projection, extending the doubling period to approximately every two years. This revision, later formalised as Moore's Law by Caltech professor Carver Mead, became the semiconductor industry's dominant planning instrument for nearly five decades — a shared commitment that aligned capital expenditure, fabrication investment, and device architecture roadmaps across competing manufacturers.

What Drives the Density Increase?

The mechanism underpinning transistor density scaling is photolithography: the process by which patterns are optically projected onto a photosensitive chemical layer on a silicon wafer. Reducing the wavelength of the illumination source directly reduces the minimum resolvable feature size. The industry progressed from ultraviolet mercury arc lamps (365 nm, i-line) through deep ultraviolet krypton fluoride (248 nm) and argon fluoride (193 nm) excimer laser sources, before transitioning to extreme ultraviolet (EUV) lithography at 13.5 nm, achieved by generating plasma from tin droplets struck by a high-power laser pulse.

Each wavelength reduction required fundamental redesigns of optical elements, mask materials, resist chemistry, and environmental control. Clean room particulate standards became progressively more demanding: by the 300 mm wafer era, acceptable contamination levels were measured in particles per cubic metre at sub-100 nm sizes, requiring wafer handling in environments cleaner than operating theatres by orders of magnitude.

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year... Certainly over the short term this rate can be expected to continue, if not increase." — Gordon Moore, 1965

The Physical Limits Begin to Appear

Throughout the 1990s and early 2000s, the primary challenge was economic: photolithographic tool sets were expensive, and each node transition required substantial capital investment. The physics remained cooperative. By the mid-2000s, however, fundamental physical constraints began to assert themselves in ways that simple engineering investment could not resolve.

The gate dielectric — the insulating layer between the polysilicon gate electrode and the silicon channel — had been constructed from silicon dioxide since the earliest MOSFET devices. As gate length shrank below 100 nm, the corresponding oxide thickness dropped below 2 nm. At this scale, quantum mechanical tunnelling — the ability of electrons to traverse a classically forbidden potential barrier — produced measurable leakage current through the gate oxide even when the transistor was nominally switched off. A 1.2 nm silicon dioxide layer, approximately 4–5 atomic monolayers thick, passed significant current through direct tunnelling, increasing standby power consumption dramatically and rendering further oxide thinning physically impractical.

| Process Node | Approx. Gate Length | Gate Oxide Thickness | First Commercial |

|---|---|---|---|

| 250 nm | ~180 nm | ~5.5 nm SiO₂ | 1997 |

| 130 nm | ~90 nm | ~2.5 nm SiO₂ | 2001 |

| 65 nm | ~35 nm | ~1.8 nm SiO₂ | 2005 |

| 45 nm | ~25 nm | High-k HfO₂ | 2007 |

| 10 nm | ~7 nm | Multi-layer High-k | 2017 |

| 3 nm | ~12 nm effective | Gate-All-Around | 2022 |

High-k Dielectrics and the Material Science Response

The resolution to the gate oxide tunnelling crisis came through material substitution rather than dimensional scaling. In 2007, the 45 nm generation introduced hafnium oxide (HfO₂) as the gate dielectric material. Hafnium oxide possesses a dielectric constant (k) of approximately 20–25, compared to 3.9 for silicon dioxide. A physically thicker hafnium oxide layer can achieve the same electrostatic capacitance as a much thinner silicon dioxide film, suppressing tunnelling current while maintaining the gate's ability to control channel charge.

The adoption of high-k dielectric required simultaneous replacement of the polysilicon gate electrode — which had been used since the self-aligned gate process was developed in the late 1960s — with metal gate materials capable of appropriate work functions for both n-type and p-type transistors. This gate-last integration process, developed independently at Intel and IBM, represented the most significant change in MOSFET process architecture in over thirty years.

Three-Dimensional Architecture as a Response to Planar Limits

The second structural response to physical limits was dimensional: by extruding the transistor channel into a three-dimensional fin geometry, the FinFET (Fin Field-Effect Transistor) architecture allowed gate control from three sides rather than one, dramatically reducing the off-state current while maintaining adequate on-state drive current at reduced supply voltages. FinFETs were introduced at the 22 nm generation and remained the dominant transistor architecture through the 5 nm node.

The successor geometry, gate-all-around (GAA) nanosheet transistors, wraps the gate electrode completely around a stacked series of silicon nanosheets, providing four-sided gate control. This architecture, commercialised at the 3 nm generation, represents the current state of the art in planar-to-fin-to-nanosheet architectural progression.

The Status of Moore's Law in 2026

Contemporary industry roadmaps acknowledge that the historical doubling rate has slowed significantly. The International Roadmap for Devices and Systems (IRDS) projects continued transistor density improvements, but through three-dimensional stacking, advanced packaging, and heterogeneous chiplet integration rather than through simple planar gate shrinkage. The economic periodicity of node transitions has also stretched: whereas 130 nm to 90 nm to 65 nm transitions occurred at roughly 18-month intervals in the early 2000s, recent sub-5 nm nodes have required 24 to 36 months between commercial availability milestones.

Moore's original observation remains historically accurate for the period it described. Its continued validity as a predictive tool has become increasingly qualified — a testament not to the failure of ingenuity, but to the finite dimensions of the silicon atom itself.