Reference Archive — Semiconductor Dictionary

The Semiconductor

The Semiconductor

Physics Glossary

An alphabetical reference covering 80+ terms in semiconductor physics, photolithography, microarchitecture, and materials science. Compiled for engineers, historians, and informed general readers.

A

- Acceptor Impurity

- A trivalent dopant atom (boron, gallium, indium) introduced into a semiconductor crystal that accepts electrons from the valence band, creating holes and producing p-type material. Acceptor atoms have one fewer valence electron than the host silicon lattice, resulting in a positively charged hole carrier for each dopant atom incorporated.

- Accumulation Layer

- In a metal-oxide-semiconductor (MOS) structure, the condition in which majority charge carriers accumulate at the semiconductor surface when the applied gate voltage enhances carrier density beyond equilibrium. In a p-type semiconductor with negative gate bias, holes accumulate at the silicon-oxide interface, increasing conductivity in the surface region.

- Annealing

- A controlled thermal process applied to silicon wafers after ion implantation to electrically activate dopant atoms and repair crystallographic damage caused by the implantation process. Rapid thermal annealing (RTA) heats wafers to 900–1100°C for seconds, minimising dopant diffusion while achieving high activation efficiency.

- Architecture (Microprocessor)

- The abstract specification of a processor's instruction set, register organisation, memory addressing modes, and programmer-visible state. Architecture defines the interface between software and hardware without specifying the physical implementation. Distinct from microarchitecture, which describes the specific circuit-level realisation of an architecture.

B

- Band Gap

- The energy difference between the top of the valence band and the bottom of the conduction band in a semiconductor material. Silicon has a band gap of 1.12 eV at room temperature. Band gap determines intrinsic carrier concentration, optical absorption characteristics, and the maximum operating temperature of a semiconductor device.

- Bipolar Junction Transistor (BJT)

- A three-terminal semiconductor device consisting of two p-n junctions in close proximity, forming either an n-p-n or p-n-p sandwich structure. Current flow between collector and emitter is controlled by base current injection. BJTs dominated logic design in the 1960s and 1970s before CMOS displaced them in high-density digital applications due to CMOS's superior power efficiency.

- Boolean Algebra

- A branch of algebra in which variables take binary values (0 or 1) and operations are logical rather than arithmetic. Developed by George Boole in the 1840s and applied to switching circuits by Claude Shannon in 1937. The three fundamental operations — AND, OR, and NOT — are sufficient to implement any logical function and form the basis of all digital circuit design.

- Buried Oxide (BOX)

- An insulating silicon dioxide layer buried beneath a thin active silicon layer in silicon-on-insulator (SOI) substrates. The BOX layer electrically isolates the active device region from the underlying silicon handle wafer, reducing parasitic capacitances and improving switching speed and power efficiency in SOI CMOS devices.

C

- Carrier Mobility

- A measure of how quickly charge carriers (electrons or holes) move through a semiconductor under an applied electric field, expressed in cm²/(V·s). Higher mobility produces faster transistor switching. Electron mobility in silicon (~1400 cm²/V·s) is approximately three times higher than hole mobility (~450 cm²/V·s), which is why n-channel MOSFETs are generally faster than their p-channel counterparts.

- CISC (Complex Instruction Set Computing)

- A processor architecture philosophy characterised by a large instruction set with variable-length encodings, multiple addressing modes, and instructions capable of performing complex operations — including memory access — in a single instruction. The x86 architecture is the dominant CISC lineage. Modern CISC implementations translate complex instructions into simpler internal micro-operations before execution.

- CMOS (Complementary Metal-Oxide-Semiconductor)

- A logic family using complementary pairs of p-channel and n-channel MOSFETs to implement logic gates. CMOS gates draw near-zero static current because at any steady state, one transistor type is off. Dynamic power dissipation (P = C·V²·f) scales with switching activity, making CMOS ideal for high-density integration where most gates are idle at any given moment.

- Crystal Lattice

- The periodic three-dimensional arrangement of atoms in a crystalline solid. Silicon crystallises in a diamond cubic structure with a lattice constant of 5.431 Å at room temperature. The perfection of the silicon crystal lattice — measured by defect density and crystallographic orientation — is critical to semiconductor device performance, and wafer manufacturers achieve defect densities below one defect per square centimetre.

- Czochralski Process

- The dominant method for growing single-crystal silicon ingots for semiconductor wafer manufacturing, invented by Jan Czochralski in 1916. A small seed crystal is dipped into a crucible of molten silicon at approximately 1420°C and slowly withdrawn while rotating, pulling a large cylindrical single-crystal boule. Ingots up to 300 mm in diameter and over a metre in length are routinely produced.

D

- Depletion Region

- The zone at a p-n junction from which mobile charge carriers have been swept by the built-in electric field, leaving behind ionised donor and acceptor atoms. The depletion region extends into both the n-type and p-type sides of the junction. Its width varies with applied voltage: reverse bias widens it; forward bias narrows it. The depletion region is the fundamental switching element in diodes and MOSFETs.

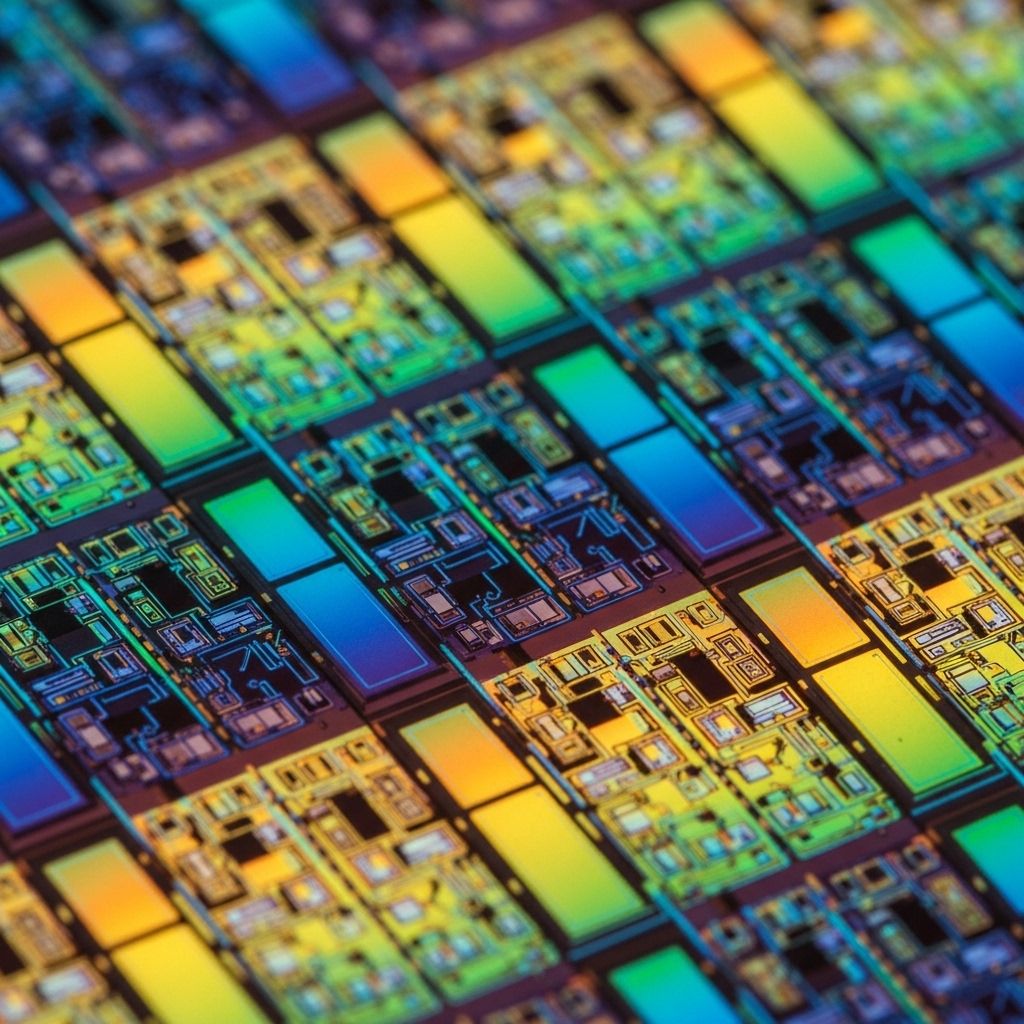

- Die

- A single rectangular section of a processed silicon wafer containing one complete integrated circuit. After wafer fabrication, individual dies are separated by a dicing process using diamond-tipped saws or laser scribing. A 300 mm wafer may contain hundreds to thousands of dies depending on die size. The term "chip" is commonly used synonymously with die.

- Donor Impurity

- A pentavalent dopant atom (phosphorus, arsenic, antimony) introduced into silicon that contributes a free electron to the conduction band, creating n-type material. Each donor atom has five valence electrons; after forming four covalent bonds with adjacent silicon atoms, the fifth electron is weakly bound and can be thermally excited into the conduction band at room temperature.

E

- Electron Volt (eV)

- The unit of energy equal to the work done on an electron when accelerated through a potential difference of one volt (1.602 × 10⁻¹⁹ joules). Used universally in semiconductor physics to express band gap energies, carrier kinetic energies, and photon energies in the context of optical processes. Silicon's band gap of 1.12 eV corresponds to light absorption at wavelengths below approximately 1.1 µm.

- EUV Lithography (Extreme Ultraviolet)

- A photolithographic technique using 13.5 nm wavelength light (produced by a laser-excited tin plasma) to pattern features at the sub-10 nm scale on silicon wafers. EUV requires near-vacuum optical paths because EUV photons are strongly absorbed by air and conventional optical materials. Reflective optics coated with molybdenum/silicon multilayer mirrors are used in place of refractive lenses.

F

- FinFET (Fin Field-Effect Transistor)

- A three-dimensional transistor geometry in which the conducting silicon channel is shaped as a narrow vertical fin, with the gate electrode wrapping around three sides (top and both lateral faces) of the fin. FinFET geometry provides significantly better electrostatic gate control than planar MOSFETs at equivalent gate lengths, suppressing short-channel effects and enabling continued scaling below 22 nm. First commercialised by Intel in 2011 at the 22 nm node.

- Flatzone / Wafer Flat

- A flat segment ground along the edge of a silicon wafer to indicate crystallographic orientation and conductivity type. Wafer flats allow robotic wafer handlers to align the wafer to a reference orientation before lithographic exposure. For wafers of 200 mm diameter and above, notches replace flats as the orientation reference feature.

G

- Gate Length

- The physical dimension of a MOSFET gate electrode measured in the direction of current flow (source to drain). Gate length is the critical dimension that determines transistor switching speed and leakage current. At sub-10 nm gate lengths, quantum mechanical effects dominate device behaviour. Gate length is distinct from the process "node" designation, which is a marketing convention that no longer directly corresponds to a physical dimension.

- Gate Oxide

- The thin insulating layer separating the gate electrode from the silicon channel in a MOSFET. Traditionally thermally grown silicon dioxide (SiO₂), gate oxide thickness scales with transistor geometry — reaching 1.2 nm (approximately 5 atomic layers) at the 90 nm node. At such thicknesses, quantum mechanical tunnelling through the oxide produces unacceptable gate leakage current, driving the adoption of high-k dielectric materials (hafnium oxide) as gate oxide replacements from the 45 nm node onward.

H

- High-k Dielectric

- An insulating material with a dielectric constant (k) greater than that of silicon dioxide (k ≈ 3.9), used as a gate insulator replacement in advanced CMOS processes. Hafnium oxide (HfO₂, k ≈ 25) allows a physically thicker gate insulator to achieve the same capacitive coupling as an ultra-thin SiO₂ layer, eliminating tunnelling leakage while maintaining transistor control. Introduced at the 45 nm node in commercial production.

- Hole

- A quasi-particle representing the absence of an electron in the valence band of a semiconductor. Holes behave as positively charged carriers with a positive effective mass. Under an applied electric field, holes drift in the direction of the field (opposite to electron drift), contributing to current flow in p-type semiconductors and the p-channel transistors of CMOS logic.

I

- Integrated Circuit (IC)

- A miniaturised electronic circuit fabricated on a single semiconductor substrate, typically silicon, in which transistors, resistors, capacitors, and interconnects are formed by successive deposition, doping, and etching processes. The integrated circuit was independently conceived and demonstrated by Jack Kilby at Texas Instruments and Robert Noyce at Fairchild Semiconductor in 1958–1959, fundamentally enabling the scaling trajectory described by Moore's Law.

- Ion Implantation

- A process for introducing controlled quantities of dopant impurities into a semiconductor substrate by accelerating ionised dopant atoms to energies of 10 keV to several MeV and directing them into the wafer surface. Implanted ions come to rest at a mean depth determined by their mass and the implantation energy. Ion implantation offers precise dose control and sharp dopant profiles unattainable by thermal diffusion alone.

J

- Junction Temperature

- The operating temperature of the p-n junction within a semiconductor device, a critical parameter for device reliability and lifetime. Junction temperature rises with power dissipation and thermal resistance of the packaging and heatsink assembly. Exceeding the maximum rated junction temperature accelerates electromigration in metal interconnects, oxide degradation, and hot carrier injection damage.

L

- Leakage Current

- Undesired current flow through a semiconductor device when it is nominally in the off state. In sub-10 nm MOSFET transistors, leakage mechanisms include subthreshold leakage (carrier diffusion below threshold voltage), gate oxide tunnelling leakage, and junction leakage. As transistor counts per chip have reached billions, aggregate leakage current constitutes a significant fraction of total chip power dissipation even at zero switching activity.

- Logic Gate

- A fundamental electronic circuit that implements a Boolean logic operation on one or more binary inputs to produce a binary output. The six universal logic gate types are: AND, OR, NOT (inverter), NAND, NOR, and XOR. Any Boolean function, however complex, can be implemented as a network of NAND or NOR gates alone, making these "universal" gates. Modern logic gates are implemented in CMOS technology.

M

- Metal Interconnect

- The network of metallic conductors fabricated above the transistor layer to electrically connect devices within an integrated circuit. Modern processors contain 10–15 interconnect layers, predominantly copper (introduced at the 130 nm node, replacing aluminium for its lower resistivity), separated by low-k dielectric materials. Interconnect delay and resistance increasingly dominate circuit performance at advanced nodes.

- Moore's Law

- The empirical observation by Gordon Moore (1965) that the number of transistors on an integrated circuit doubles approximately every two years. Originally a two-year doubling; subsequently revised to 18 months as a more commonly cited figure. Moore's Law has guided semiconductor industry roadmaps for six decades, though physical scaling constraints at sub-5 nm dimensions have made continued density doubling increasingly challenging and expensive.

- MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor)

- The dominant transistor type in contemporary integrated circuits. A voltage applied to the insulated gate electrode modulates the conductivity of the semiconductor channel between source and drain terminals. MOSFETs operate as voltage-controlled switches: gate voltage exceeding a threshold value (Vth) inverts the channel, allowing current to flow. The gate draws negligible steady-state current due to the insulating oxide layer.

N

- N-Type Semiconductor

- Silicon doped with donor impurities (phosphorus, arsenic) such that free electrons are the majority charge carriers. The "n" designation refers to the negative charge of the electron majority carriers. N-type material has its Fermi level shifted toward the conduction band compared to intrinsic silicon.

- Nanometre Node

- A designation used by semiconductor foundries to label successive generations of manufacturing technology, historically corresponding approximately to the minimum transistor feature size or gate length. Since the 22 nm node, the node designation has become a marketing label without direct correspondence to a single physical dimension — a 7 nm process may have gate lengths of 12–18 nm in practice.

P

- Photolithography

- The process of transferring a geometric pattern from a photomask to a photosensitive chemical film (photoresist) on a silicon wafer using light. An optical system projects the mask pattern onto the resist layer; exposed regions undergo a chemical change that allows selective removal, defining the boundaries of subsequent etching or deposition steps. Repeated across 10–20 mask layers, photolithography builds up the complete three-dimensional structure of an integrated circuit.

- Photoresist

- A light-sensitive polymer coating applied to the wafer surface prior to lithographic exposure. Positive photoresists become soluble in developer solution upon exposure to light (exposed areas are removed); negative photoresists polymerise upon exposure, becoming insoluble. The patterned photoresist acts as a physical mask for subsequent etching and ion implantation steps.

- P-N Junction

- The interface between p-type and n-type semiconductor regions within a single crystal, formed by adjacent differently-doped regions. The p-n junction is the fundamental building block of semiconductor devices: it exhibits rectifying behaviour (conducting in one direction, blocking in reverse), generates the built-in electric field that drives carrier separation in photodetectors and solar cells, and forms the switching element in bipolar transistors.

Q

- Quantum Tunnelling

- A quantum mechanical phenomenon in which a particle traverses an energy barrier that classical mechanics would forbid it from crossing, due to the wave-like nature of quantum particles. In semiconductor devices, quantum tunnelling of electrons through ultra-thin gate oxide layers and through the gate length itself becomes significant below 10 nm dimensions, producing leakage currents that increase exponentially as feature sizes decrease.

R

- RISC (Reduced Instruction Set Computing)

- A processor architecture philosophy characterised by a small, fixed-length instruction set, load-store memory access model (arithmetic operates only on registers), and large general-purpose register files. RISC architectures — including MIPS, SPARC, and ARM — enable efficient pipelined implementation by simplifying instruction decode hardware. ARM architecture RISC processors power the majority of mobile devices worldwide.

- Resistivity

- A material property measuring how strongly a material opposes electric current flow, expressed in ohm-metres (Ω·m). Intrinsic silicon has a resistivity of approximately 640 Ω·m, between conductors and insulators. Doping reduces resistivity by many orders of magnitude: heavily doped silicon (10²⁰ cm⁻³) approaches metallic resistivity (~10⁻⁴ Ω·m), enabling doped silicon regions to function as low-resistance current paths in transistors.

S

- Silicon (Si)

- A group IV semiconductor element with atomic number 14, the dominant material of the modern semiconductor industry. Silicon's band gap of 1.12 eV is well matched to room-temperature electronic device operation; it forms a stable, high-quality native oxide (SiO₂) useful as a gate insulator; and it is the second most abundant element in the Earth's crust. The Czochralski process produces single-crystal silicon ingots of exceptionally high purity (less than one part per billion impurities).

- Silicon Wafer

- A thin, flat disk of single-crystal silicon, polished to nanometre-scale surface flatness, on which semiconductor devices are fabricated. Wafer diameters have increased from 25 mm (1960s) to 300 mm (current production standard) and 450 mm (in development), with larger diameters yielding more dies per wafer, reducing per-die fabrication cost. Wafer thickness is typically 775 µm for 300 mm substrates.

- Subthreshold Slope

- The rate at which a MOSFET's drain current decreases per decade of gate voltage reduction below the threshold voltage, measured in mV/decade. The theoretical lower limit of subthreshold slope for a conventional MOSFET is 60 mV/decade at room temperature, set by Boltzmann thermal statistics. Achieving steep subthreshold slopes enables low-voltage operation; tunnel FETs can theoretically achieve slopes below 60 mV/decade by exploiting band-to-band tunnelling mechanisms.

T

- Threshold Voltage (Vth)

- The minimum gate-to-source voltage required to create a conducting inversion channel in a MOSFET and allow significant drain current to flow. Threshold voltage is a critical design parameter: too high, and it limits operating speed and supply voltage scaling; too low, and subthreshold leakage increases power dissipation. Threshold voltage is engineered through substrate doping concentration, gate oxide thickness, and gate metal work function.

- Transistor

- A three-terminal semiconductor device that can amplify or switch electronic signals. The bipolar junction transistor (BJT), invented at Bell Laboratories in 1947, and the metal-oxide-semiconductor field-effect transistor (MOSFET), first demonstrated in 1960, are the two dominant transistor families. MOSFETs constitute the fundamental switching element of all modern digital logic and memory, with over one sextillion (10²¹) MOSFETs manufactured annually as of the mid-2020s.

V

- Valence Band

- The highest energy band in a semiconductor that is fully occupied by electrons at absolute zero temperature. Electrons in the valence band are bound to atomic sites and do not contribute to electrical conduction. When electrons are thermally excited or optically promoted across the band gap into the conduction band, they leave behind positively charged holes in the valence band that contribute to hole conduction.

- VLSI (Very Large Scale Integration)

- A classification of integrated circuits containing between 100,000 and 1 million transistors, corresponding to the technology generation of the 1980s. Preceded by SSI (small-scale), MSI (medium-scale), and LSI (large-scale) integration, and followed by ULSI (ultra-large-scale) and GSI (giga-scale) designations as transistor counts per chip have reached the billions and hundreds of billions respectively.

W

- Wafer Fab (Fabrication Facility)

- A cleanroom manufacturing facility in which silicon wafers are processed through the hundreds of sequential deposition, lithographic, etching, and doping steps required to produce integrated circuits. Wafer fabs operate under ISO Class 1 cleanroom conditions (fewer than 10 particles larger than 0.1 µm per cubic metre of air), with controlled temperature, humidity, and electrostatic discharge environments. Capital cost for a leading-edge 3 nm wafer fab exceeds $10–$20 billion USD.

- Work Function

- The minimum energy required to remove an electron from a solid material to a point just outside its surface, measured in electron volts. The work function of the gate electrode material relative to the silicon channel determines the flat-band voltage and threshold voltage of a MOSFET. High-k/metal gate stacks in advanced CMOS processes use metal gate electrodes with precisely engineered work functions to achieve optimal threshold voltages for both n-channel and p-channel transistors.

Z

- Zone Refining

- A purification technique for semiconductor materials in which a narrow molten zone is passed along a rod or ingot. Impurities preferentially remain in the liquid phase (having lower segregation coefficients than the host material), and are progressively swept toward one end of the ingot by repeated passes of the molten zone. Zone refining can achieve impurity concentrations below 1 part per billion in polycrystalline silicon before Czochralski crystal growth.

Further Study

Explore the Archive

Continue your study of semiconductor history with our research journal articles, virtual exhibit collections, and the interactive microarchitecture quiz.