The Silicon

Epoch

A digital museum dedicated to the physics of semiconductors, the architecture of microprocessors, and the material heritage of computing from the relay era to the sub-nanometre gate.

Visit Virtual Exhibit

The Institute of Microcomputing History was founded with a singular conviction: that the engineering decisions made inside a silicon fabrication facility are as historically significant as any architectural, artistic, or industrial milestone. The transistor, first realised in germanium and later perfected in silicon, did not merely accelerate arithmetic — it restructured civilisation.

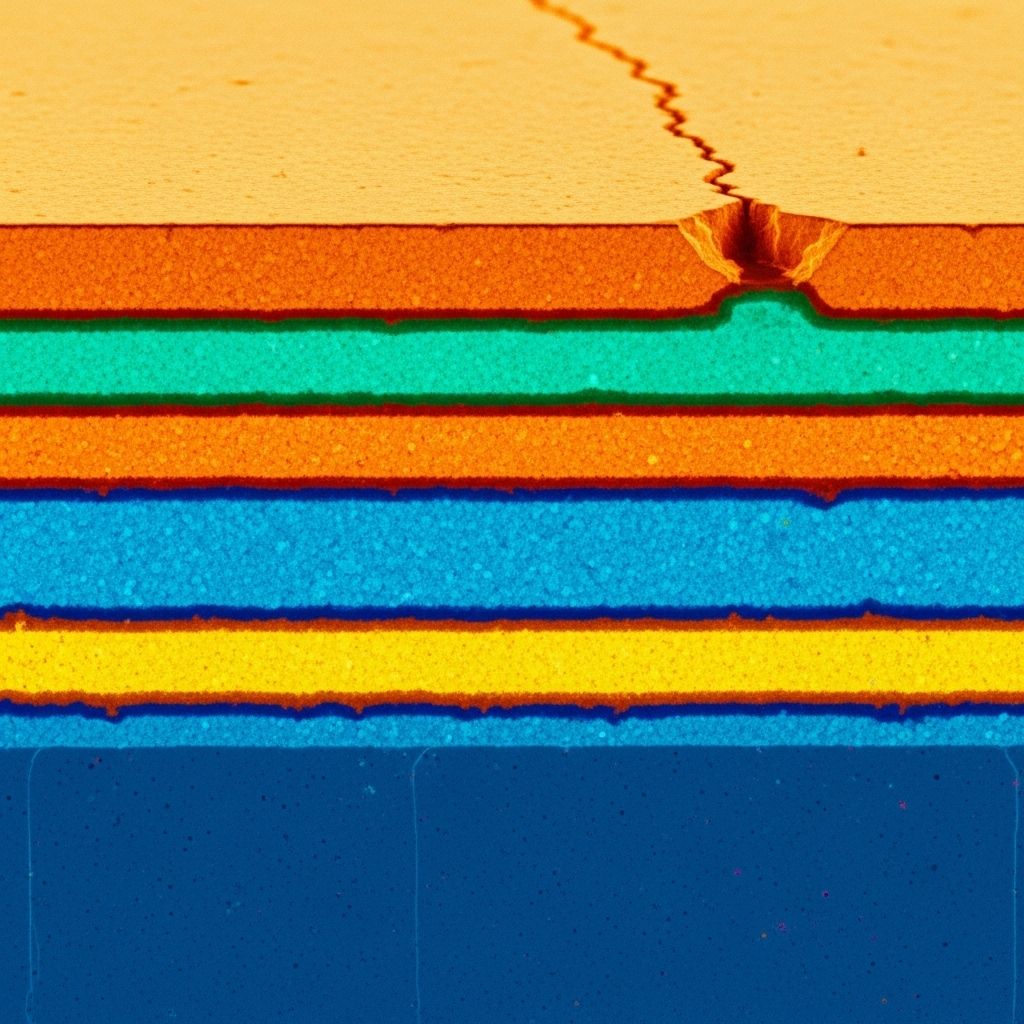

This archive curates the documented engineering record: the photolithographic processes that shrunk the gate length from micrometres to angstroms; the competing instruction set philosophies that defined two generations of processor design; the material science of boron-doped substrates and copper interconnect layers. Our approach is rigorously academic, visually cinematic, and entirely non-commercial.

We operate independently, with no affiliations to hardware manufacturers, commercial vendors, or technology service providers. Every article, exhibit, and reference entry in this archive is produced with primary-source fidelity and peer-reviewed accuracy.

ByteComputerRepairs Archive Foundation · Via della Scienza 42, Milano · March 2026

Three Epochs of Processor Evolution

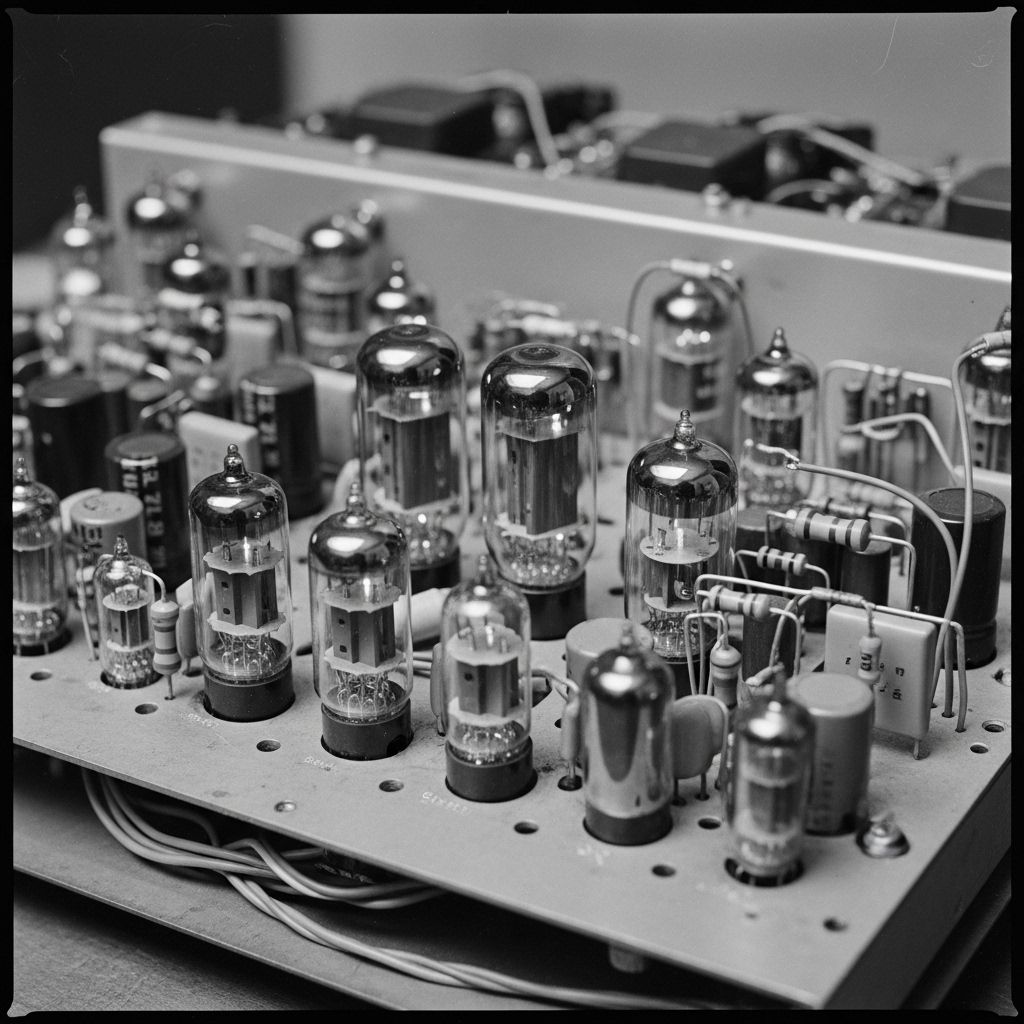

The Vacuum Tube and Transistor Transition

The invention of the bipolar junction transistor at Bell Labs in 1947 displaced thermionic vacuum tubes across logic circuitry. By 1960, planar transistor fabrication enabled the first commercial integrated circuits, collapsing the gap between discrete component assemblies and monolithic silicon.

Read the HistoryThe Microprocessor and the RISC/CISC Debate

Intel's 4004 (1971) demonstrated that an entire central processing unit could occupy a single chip. The subsequent two decades saw the crystallisation of Complex Instruction Set Computing (CISC) philosophy against the challenger paradigm of Reduced Instruction Set Computing (RISC), debated in academic literature and resolved empirically through benchmark competition.

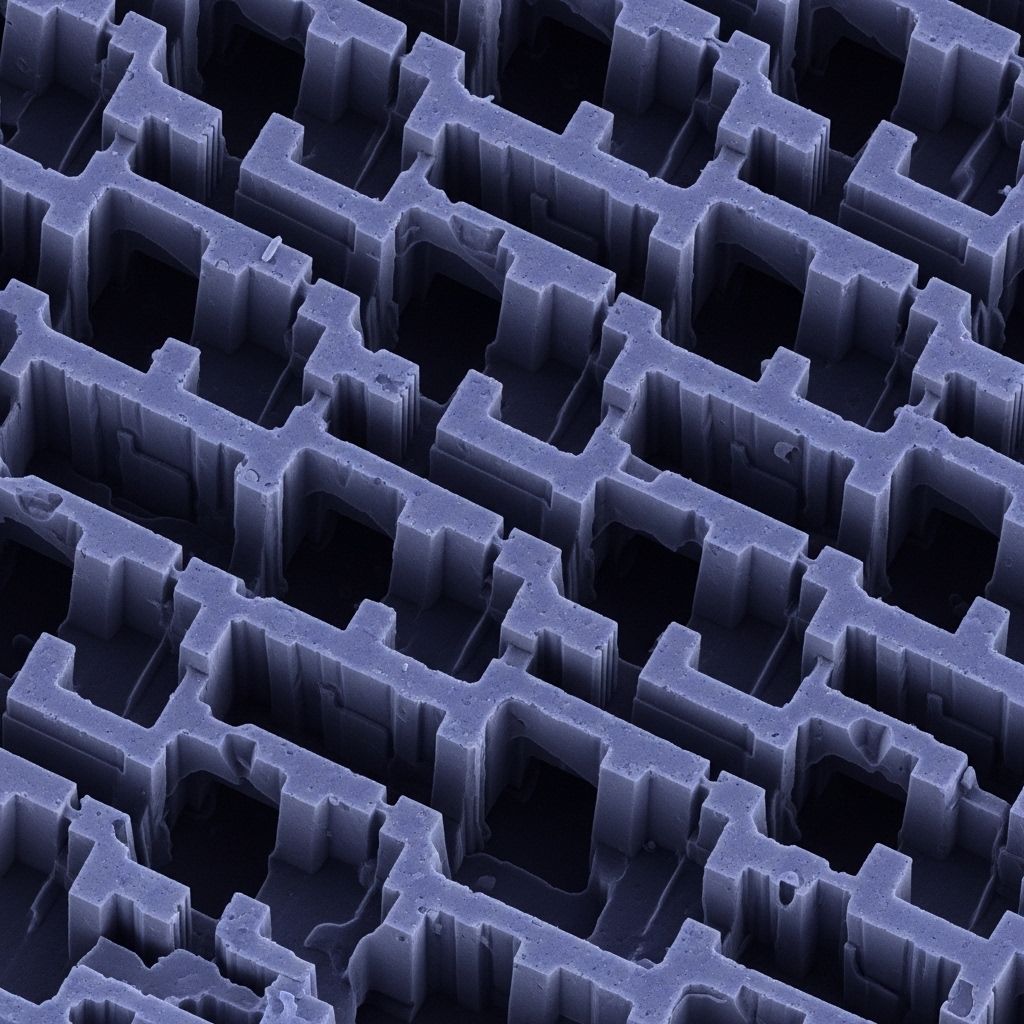

Read the Architecture ReviewThe Nanometre Frontier and Quantum Effects

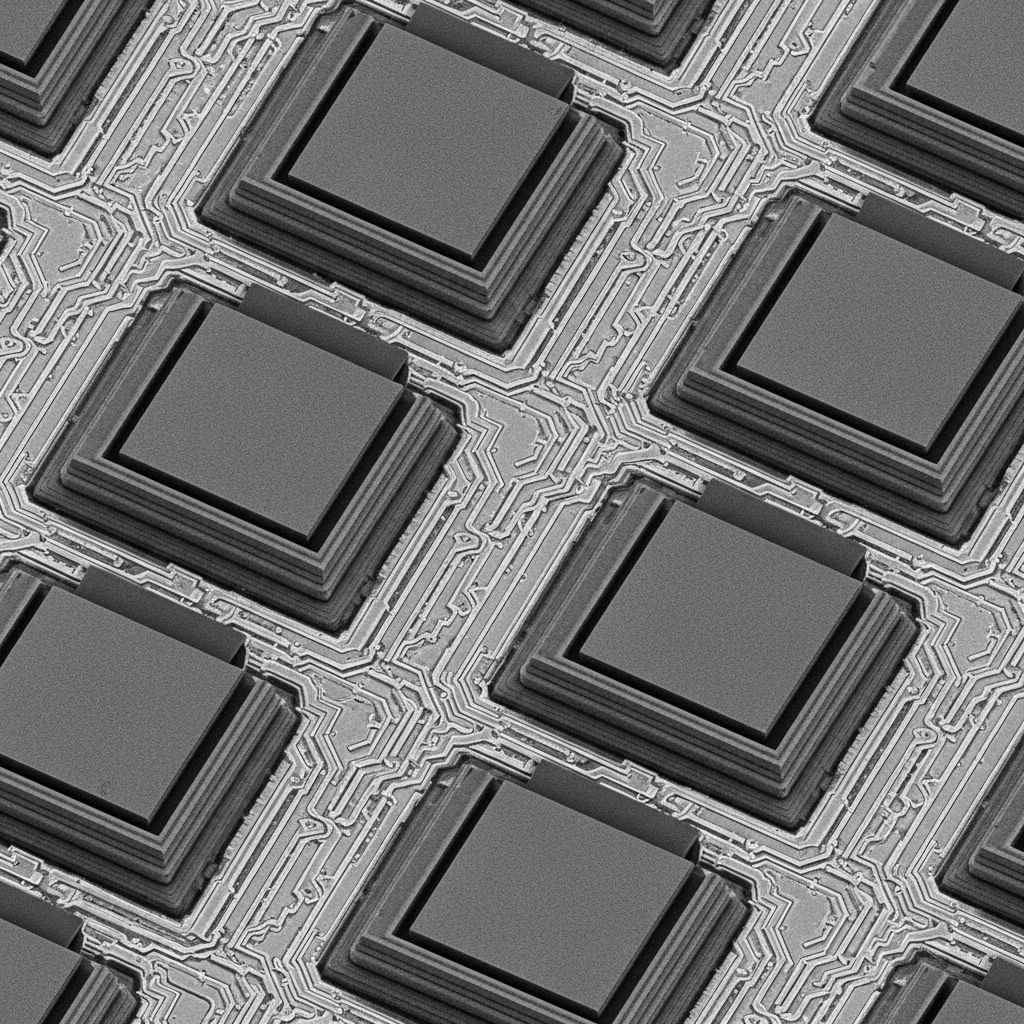

As gate lengths crossed the 10 nm threshold, quantum mechanical effects became inescapable design constraints. Tunnelling current, sub-threshold leakage, and gate-oxide breakdown demanded architectural responses: FinFET geometries, high-k dielectrics, and the exploration of alternative channel materials including silicon-germanium alloys and III-V compound semiconductors.

Explore Quantum TunnelingVirtual Exhibits

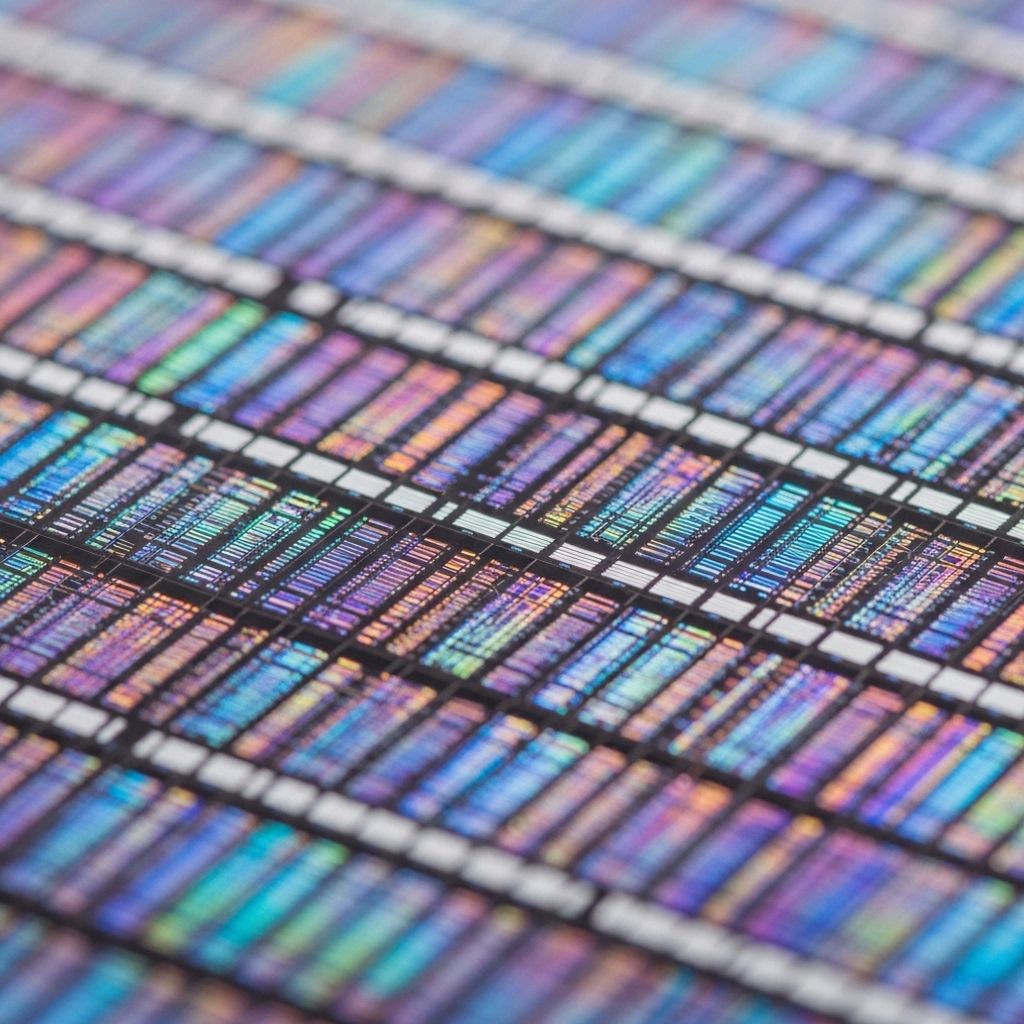

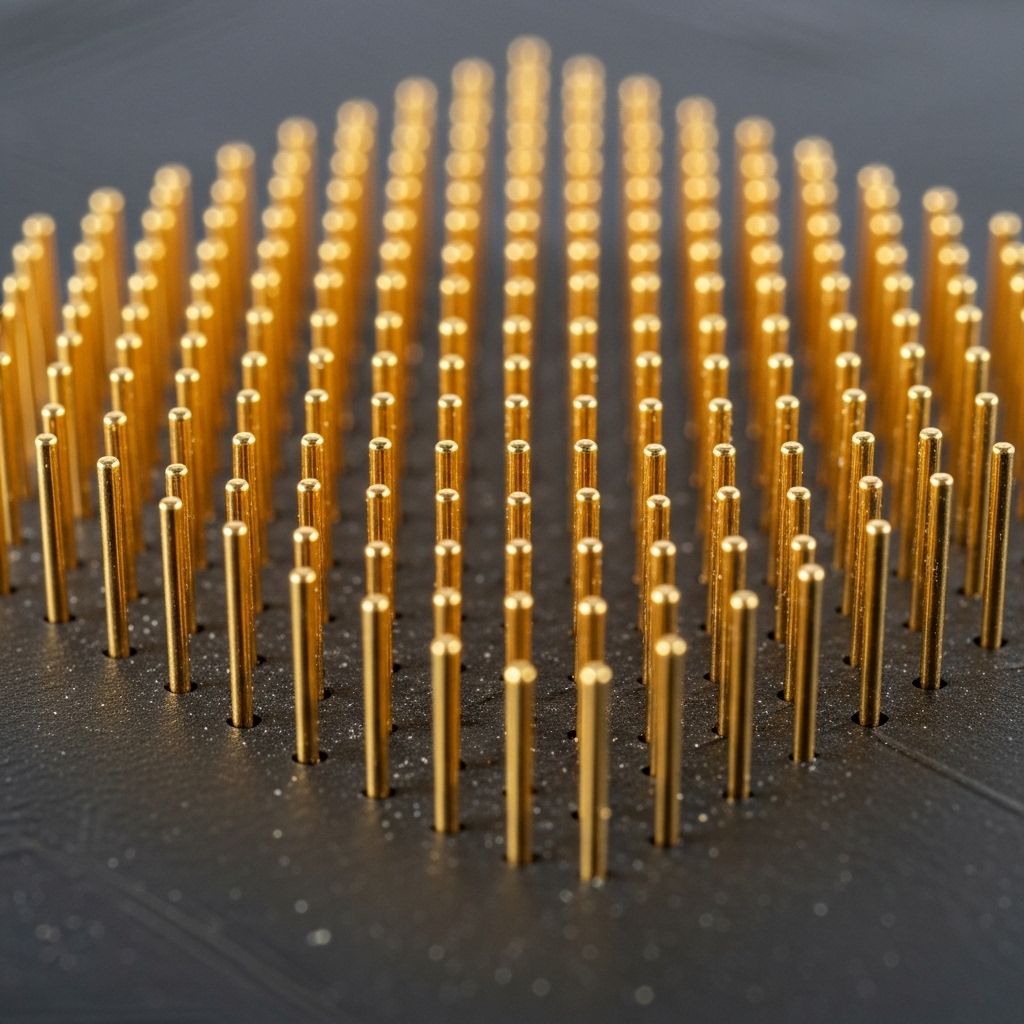

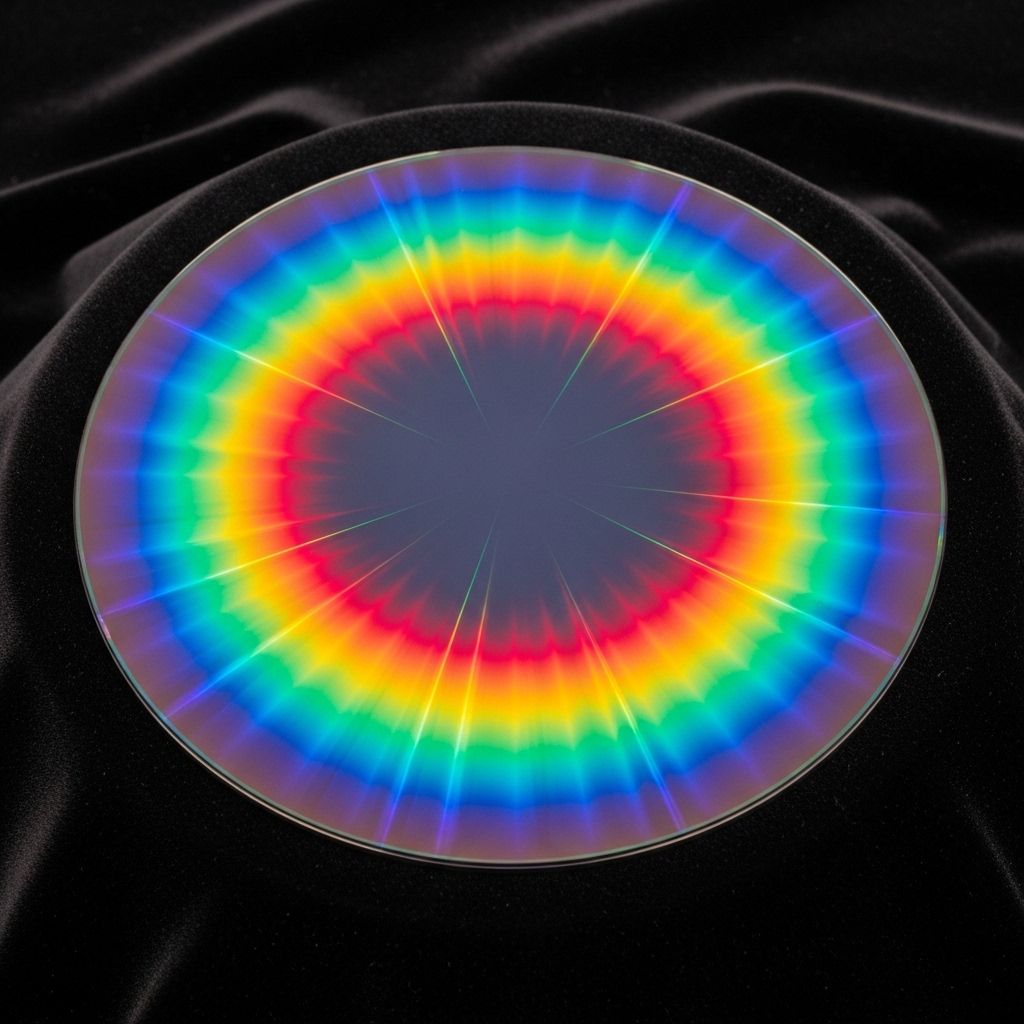

From Sand to Circuit: The Silicon Wafer Collection

Four artefacts. Four decades. The evolution of silicon substrate manufacturing from the 50mm wafers of early commercial VLSI production to the 450mm ultra-flat substrates of contemporary foundries. Each specimen is catalogued with material composition, crystallographic orientation, and manufacturing provenance.

Visit Virtual ExhibitFeatured Research Articles

- Mar 2026 Moore's Law and the Physical Limits of Silicon Semiconductor Physics

- Feb 2026 The Evolution of CISC vs RISC Architectures Microarchitecture

- Feb 2026 Quantum Tunneling: When Transistors Get Too Small Quantum Effects

- Jan 2026 Material Science of Motherboards: Fiberglass and Copper Materials Science

- Jan 2026 The History of the Logic Gate: From Relays to Silicon Logic History

Frequently Asked Questions on Processor Physics

Enter the Archives

Eighteen scholarly articles, four curated virtual exhibits, and a comprehensive semiconductor glossary — assembled for engineers, historians, educators, and everyone who understands that silicon changed everything.